Цифровой фильтр высокой частоты

Категория реферата: Рефераты по информатике, программированию

Теги реферата: база рефератов, англия реферат

Добавил(а) на сайт: Rodzjanko.

Предыдущая страница реферата | 2 3 4 5 6 7 8 9 10 11 12 | Следующая страница реферата

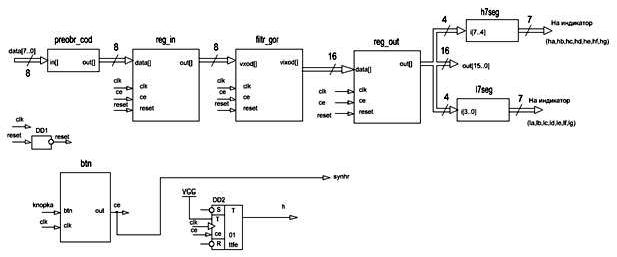

2. reg_in и reg_out –параллельные параметризированные регистры

3. preobr_cod – преобразователь кода , предназначен для преобразования входного прямого кода в дополнительный код;

4. filter_gor – основной блок преобразования

5. tffe-триггер

6. l7segment и h7segment – семисегментные индикаторы(?!), необходимы для проверки работы устройства.

Рис.14 Структурная схема устройства

Составление и описание принципиальной схемы устройства.

Разработка и отладка программы на языке AHDL

Для конфигурирования ПЛИС семейства FLEX10K существуют следующие способы:

Пассивная последовательная (последовательное ПЗУ, ByteBlaster, BiteBlaster, JTAG, микроконтроллер);

Пассивная параллельная синхронная (микроконтроллер);

Пассивная параллельная синхронная (микроконтроллер);

В проекте будет использовано JTAG конфигурирование. Для конфигурирования посредством JTAG выводы MSEL0, MSEL1 необходимо подключить к земле.

JTAG (Joint Test Action Group) - объединенная группа по вопросам тестирования – разработала спецификации для периферийного сканирования (BST – Boundary Scan Test). BST-технология позволяет выполнить эффективное тестирование компонентов на прецизионных печатных платах. BST-технология может тестировать выводы без использования щупов и пробников и выполняет сбор необходимых функциональных данных в нормальном режиме функционирования микросхемы. Для работы в JTAG-режиме используются четыре выделенных вывода: TDI, TDO, TMS, и TCK, и вспомогательный вывод TRST. Все остальные выводы во время JTAG-конфигурирования находятся в третьем состоянии. JTAG-конфигурирование нельзя начинать до завершения других режимов конфигурирования. Во время JTAG-конфигурирования конфигурационные данные загружаются в микросхему на печатной плате через разъемы кабелей MasterBlaster или ByteBlasterMV.

1)TDI – Вход тестовых данных.( Вход последовательной загрузки инструкций, программирующих и тестовых данных. Данные синхронизируются фронтом импульсов на выводе TCK.)

2)TDO – Выход тестовых данных.( Последовательный выход инструкций, программирующих и тестовых данных. Данные синхронизируются спадом импульсов на выводе TCK. Если данные из микросхемы не поступают - вывод находится в третьем состоянии)

3)TMS – Выбор режима тестирования (режим контроллера BST)( Вход управления режимом конечного автомата (контроллера) TAP. Конечный автомат синхронизируется фронтом сигнала на входе TCK. Поэтому состояние вывода TMS должно быть установлено перед фронтом сигнала TCK.)

4)TCK – Тактовый вход контроллера BST(Тактовый синхровход схемы BST. Некоторые операции синхронизируются фронтом, а некоторые спадом сигнала на TCK.)

5) TRST– Вход прекращения тестирования (дополнительный)( Вход асинхронного сброса схемы периферийного сканирования."0" на выводе – сбрасывает BST-схему периферийного сканирования. Вывод TRST является дополнительным в соответствии со стандартом IEEE STD. 1149.1.)[2]

(Какое отношение имеет выделенный материал к разделу??)

При разработке программы потребовалось написать на языке AHDL следующие модули:

1)Преобразователь кода из прямого в дополнительный(Имя?):

Если старший бит входных данных равен нулю, то код не изменяется, если равен единице,то все разряды кроме старшего инвертируются, а затем к младшему прибавляется единица.

2)Антидребезговая схема(Имя?):

Рекомендуем скачать другие рефераты по теме: дипломная работа скачать бесплатно, реферат бесплатно на тему.

Предыдущая страница реферата | 2 3 4 5 6 7 8 9 10 11 12 | Следующая страница реферата