Процессор К1810ВМ89

Категория реферата: Рефераты по информатике, программированию

Теги реферата: конспект урока 5 класс, реферат диагностика

Добавил(а) на сайт: Крюков.

1 2 | Следующая страница реферата

Общие сведения и технические характеристики специализированного процессора вводаа-вывода К1810ВМ89

Микросхема К1810ВМ89 представляет собой однокристальный 20-битовый специализированный процессор ввода — вывода (СПВБ), выполненный по высококачественной n-МОП -технологии [4, 5, 15]. Кристалл микросхемы размером 5,5*5,5 мм потребляет мощность не более 2.5 Вт от источника питания напряжением +5 В. Схема выпускается в 40-выводном корпусе. Синхронизуется однофазными импульсами с частотой повторения 1—5 МГц от внешнего тактового генератора.

Процессор К1810ВМ89 (обозначаемый далее для краткости ВМ89) используется совместно с центральным процессором ВМ86ВМ88, а также К580ВМ80. Он предназначен для повышения производительности систем на базе МПК К1810 благодаря освобождению ЦП от управления вводом — выводом и осуществлению высокоскоростных пересылок с прямым доступам в память (ПДП пересылок). К основным функциям СПВБ ВМ89 относятся инициализация и управление контроллерами внешних устройств, обеспечение гибких и универсальных пересылок с ПДП. Процессор может работать параллельно с ЦП одновременно по двум каналам ввода — вывода, каждый из которых обеспечивает скорость передачи информации до 1,25 Мбайт/с при стандартной тактовой частоте 5 МГц. Организация связи СПВВ с центральным процессором через память повышает гибкость взаимодействия и облегчает создание модульного программного обеспечения, что повышает надежность разрабатываемых схем.

Процессор ВМ89 имеет два идентичных канала ввода — вывода, каждый из которых содержит 5 20-битовых, 4 16-битовых и один 4-битовый регистр. Взаимодействие каналов при параллельной работе осуществляется под управлением встроенной логики приоритетов. Процессор обеспечивает 16-битовую шину данных для связи с ОЗУ и портами ВВ. Шина адреса имеет 20 линий, что позволяет непосредственно адресоваться к памяти емкостью до 1 Мбайт. Для экономии числа выводов БИС младшие 16 адресных линий мультиплексированы во времени с линиями данных и составляют единую локальную шину адреса/данных. Четыре старшие адресные линии аналогично мультиплексированы с линиями состояния СПВБ. Чтобы сигналы этих линий можно было использовать в МПС, их обязательно демультиплексируют, либо с помощью тех же внешних схем, которые используются ЦП (в местной конфигурации), либо с помощью независимых схем (в удаленной конфигурации).

Система команд СПВВ ВМ89 содержит 53 мнемокода, причем возможности и набор команд оптимизированы специально для гибкой, эффективной и быстрой обработки данных при вводе — выводе. СПВБ позволяет сопрягать 16- и 8-битовые шины и периферийные устройства. При использовании ВМ89 в удаленном режиме пользователь программно может определить различные функции шины СПВБ, легко сопрягая ее со стандартной шиной Multibus.

Предельно допустимые условия эксплуатации БИС К1810ВМ89: температура окружающей среды 0...70 °С, напряжение на любом выводе относительно корпуса -0.3 ...+7В. Основные хар-ки по постоянному току при- ведены в табл. 1

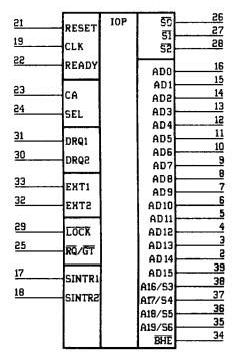

Назначение выводов БИС К1810ВМ89

| Параметр | Значение параметра Условия | Условия измерения | |

| min | мах | ||

| Напряжение "0" на входе, В | -0,5 | +0,8 | |

| Напряхение "1" на входе, В | 2,0 | 6,0 | |

| Напряжение "0" на выходе, В | 0,45 | I=2,0 мА | |

| Напряжение "1" на выходе, В | 2,4 | I=-0.4 мА | |

| Ток источника питания, мА | 350 | Т=25 С | |

| Ток утечки на входах, мкА | ±10 | Uвх=5 В | |

| Ток утечки на выходах, мкА | ±10 | 0,45£U вых³5 В | |

| Напряжение "0" на входе тактовой частоты, В | -0,5 | +0,6 | |

| Напряжение "1" на входе тактовой частоты, В | 3,6 | 6,0 | |

| Емкость входа (для всех вы- водов, кроме ADO - AD15, RQ/GT), пф | F=1MГц | ||

| Емкость входа/выхода ADO - AD15, RQ/GT. пф | F=1MГц | ||

|

AD15-AD0 - входы выходы для формирования адресов и передачи данных. Функции этих линий задаются сигналами состояния до S2, SI, SO. Линии находятся в высокоомном состоянии после общего сброса, и тогда, когда шина не используется. Линии AD15—AD8 формируют стабильные (не мультиплексированные) сигналы при пересылках на 8-битовую физическую шину данных и мультиплексируются с данными при пересылках на 16-битовую физическую шину данных (таб 1).

A19/S6, A18/S5, A17/S4, A16/S3 - выходы для формирования четырех старших разрядов адресов и сигналов состояний. Сигналы адресов формируются в течение первой части цикла шины (Т1), в остальной части цикла активны сигналы состояний, которые кодируются так: S6=S5=1 - означает ПДП-пересылку; S4=0, что означает ПДП-пересылку; S4=l— цикл шины без ПДП; S3=0—работает канал 1; S3=l—работает канал 2. После такого сброса при отсутствии обращений к шине эти линии находятся в высокоомном состоянии.

ВНЕ - выходной сигнал разрешения старшего байта шины данных. Сигнал низкого (активного) уровня формируется процессором, когда байт должен передаваться по старшим линиям D15 — D8. После общего сброса и. при отсутствии обращений к шине этот выход находится в высокоомном состоянии. Сигнал ВНЕ (в отличие от аналогичного сигнала процессоров ВМ86 и ВМ87) может не фиксироваться в фиксаторе адреса, так как он не мультиплексирован с другим сигналом.

S2-S0 - выходы для кодирования стояния ВМ89, определяющие действия процессора в каждом цикле работы с шиной. Они кодируются следующим образом: S2S1S0=000—выборка команды из адресного пространства ввода — вывода; 001-чтение данных из адресного пространства ввода—вывода; 010—запись данных в адресное пространство ввода-вывода; 100-выборка команды из системного пространства адресов; 101-чтение данных из системного пространства адресов; 101 — чтение данных из системного пространства адресов; 110-зщапись данных в системное пространство адресов; 111 — пассивное состояние. Код 01l—не используется. С помощью этих сигналов контроллер шины и арбитр шины формируют команды управления памятью и устройствами ввода-вывода. Сигналы формируются в такте Т4 предыдущего цикла, определяя начало нового цикла. По окончании цикла шины в такте Т3 или ТW сигналы возвращаются в пассивное состояние. После общего сброса и при отсутствии обращений к шине выходы S2, SI, SO находятся в высокоомном состоянии.

READY — входной сигнал готовности, поступающий от адресуемого устройства, которое оповещает СПВБ о том, что оно готово к пересылке данных. Сигнал синхронизируется в тактовом генераторе К1810ГФ84.

LOCK — выходной сигнал монополизации (блокировки) системной шины. Используется в многопроцессорных системах и подается на одноименный вход арбитра шины К1810ВБ89, запрещая доступ к системной шине другим процессорам. Сигнал формируется установкой соответствующего разряда регистра управления канала либо командой TSL. После общего сброса и при отсутствии обращений к шине выход LOCK находится в высокоомном состоянии.

RESET — входной сигнал общего сброса (начальной установки) останавливает любые действия СПВБ и переводит его в пассивное состояние до получения сигнала запроса готовности канала.

CLK — вход для подачи импульсов синхронизации от генератора тактовых К1810ГФ84.

СА — входной сигнал запроса готовности канала. Используется центральным процессором для инициализации СПВВ и определения задания каналам. По срезу сигнала СА опрашивается состояние входа SEL.

SEL – входной сигнал, который по первому (после общего сброса) сигналу СА определяет статус (ведущий/ведомый) СПВБ и запускает последовательность инициализации. При поступлении последующих сигналов СА сигнал SEL определяет номер канала (1 или 2), которому предназначено сообщение от ЦП.

DRQ1, DRQ2 – входы запросов прямого доступа к памяти от внешних устройств. Сигналы на этих входах сигнализируют СПВВ, что внешнее устройство готово к обмену данными с использованием канала 1 или 2 соответственно.

RQ/GT — входной/выходной сигнал запроса/предоставления шины, по которому осуществляется диалог, необходимый для арбитража шины между СПВВ и ЦП в местной конфигурации или между двумя СПВВ в удалённой конфигурации.

SINTR1, SINTR2 – выходные сигналы запросов прерываний от каналов 1 и 2 соответственно. Обычно они передаются на вход ЦП через контроллер прерываний К1810ВН59А. Используются для сигнализации о том, что произошли задаваемые пользователем (программистом) события.

ЕХТ1, ЕХТ2 — входы сигналов внешнего окончания прямого доступа для каналов 1 и 2 соответственно. Они вызывают окончание текущей ПДП- пересылки в канале, который запрограммирован для анализа окончания ПДП по внешнему сигналу.

Структура СПВБ

Внутренняя структура СПВВ подчинена его основному назначению - выполнять пересылки данных без непосредственного вмешательства ЦП, который связывается с СПВБ только для инициализации и выдачи задания на обработку. В обоих случаях ЦП предварительно готовит необходимое сообщение в памяти и затем с помощью сигнала запроса готовности канала активизирует СПВБ ВМ89 на выполнение действий, определенных в сообщении. С этого момента СПВВ работает независимо от ЦП. В процессе выполнения задания или по его завершении СПВБ может связаться с ЦП с помощью сигнала запроса прерывания.

Процессор может обращаться к памяти и устройствам ввода — вывода (УВВ), размещенным в системном пространстве адресов емкостью 1 Мбайт или в пространство ввода – вывода ёмкостью 64 Кбайт (рис 4.2). Хотя СПВВ располагает только одной физической шиной данных, удобно полагать, что в системное пространство он обращается по системной шине (СШ) данных,

Рекомендуем скачать другие рефераты по теме: ответы гиа, мировая торговля.

1 2 | Следующая страница реферата