Процессор К1810ВМ89

Категория реферата: Рефераты по информатике, программированию

Теги реферата: рефераты, шпаргалки скачать бесплатные шпаргалки

Добавил(а) на сайт: Bronislava.

Предыдущая страница реферата | 1 2 3 4 5 6 7 8 9 10 11 | Следующая страница реферата

|

|

|

|

.

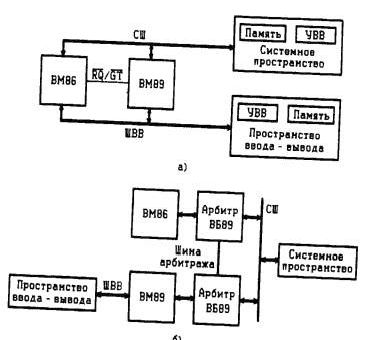

Рис 3. Использование СШ и ШВВ в местной (а) и удалённой (б) конфигурации

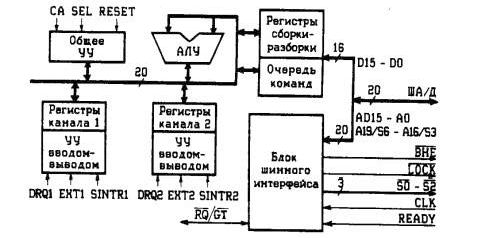

Структура процессора ввода — вывода (рис 4) включает несколько функциональных узлов, соединённых 20-битовой внутренней шиной для получения максимальной скорости внутренних пересылок. (В отличие от 16-битовой внешней шины по внутренней шине осуществляются пересылки как 16-, так и 20- битовых значений адресов и данных.)

Общее устройство управления (УУ) координирует работу функциональных узлов процессора. Все операции (выполнение команд, циклы пересылки с ПДП, ответы на запрос готовности канала и др.), выполняемые СПВВ, распадаются на последовательности элементарных действий, которые называются внутренними циклами. Цикл шины, например, составляет один внутренний цикл; выполнение команды может потребовать нескольких внутренних циклов. Всего насчитывается 23 различных типа внутренних циклов, каждый из которых занимает от двух до восьми тактов CLK (без учета возможных состояний ожидания и времени на арбитраж шин). Общее УУ указывает для каждой операции, какой функциональный узел будет выполнять очередной внутренний цикл. Например, когда оба канала активны, общее УУ определяет, какой канал имеет более высокий приоритет, либо, если их приоритеты равны, осуществляет управление попеременной работой каналов. Кроме того, общее УУ осуществляет начальную инициализацию процессора, для чего используется программно недоступный регистр ССР — указатель блока параметров.

Рис 4. Укрупненная структурная схема СПВБ ВН69

Арифметическое логическое устройство (АЛУ) может выполнять беззнаковые арифметические операции над 8- и 16-битовыми двоичными числами, включающими сложение, инкремент и декремент. Результатом арифметических операций может быть 20 - битовое число. Логические операции, включая И, ИЛИ, НЕ, могут выполняться над 8- и 16-битовыми операндами.

Регистры сборки — разборки участвует при передаче всех данных, поступающих в процессор. Когда разрядность источника и приемника данных различаются, процессор использует эти регистры для обеспечения максимальной скорости передачи. Например, при пересылке с ПДП из 8- битового УВВ в 16-битовую память процессор затрачивает два цикла шины на прием двух последовательных байтов, «собирает» их в одно 16-битовое слово и передает его в память за один цикл шины. При передаче 16- битовых данных 8- битовому приемнику осуществляется его предварительная «разборка» на байты. Таким образом, наличие регистров сборки/разборки экономит циклы шины.

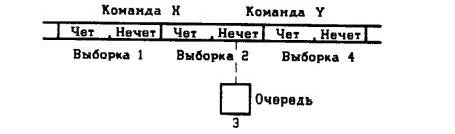

Очередь команд используется для повышения производительности процессора при выборке их из памяти. Во время выполнения программы каналом команды выбираются из памяти словами, размещёнными по чётному адресу

Рис. 5. Выборка команд с использованием очереди

младшего байта. На одну такую выборку затрачивается один цикл шины. Этот процесс показан на рис. 5. Если последний байт текущей команды Х приходится на чётный адрес, то следующий байт за ним байт из нечётного адреса (он является первым байтом команды Y) извлечённого слова в очереди. Когда канал начинает выполнять команду Y, этот байт из очереди извлекается значительно быстрее, чем из памяти. Таким образом, очередь команд размерностью всего один байт позволяет процессору при выборке команд всегда читать слова, что снижает загрузку шины, увеличивая ее пропускную способность и производительность СПВБ.

В двух исключительных случаях при извлечении команд процессор читает из памяти байты, а не слова. Во-первых, когда команда передачи управления (например, JMP, JNZ, CALL) указывает на нечётный адрес, по которому размещена команда, требующая исполнения. В этом случае первый байт команды извлекается отдельно. Во-вторых, когда встречается 6-байтовая команда LPDI, которая извлекается в следующем порядке: байт — слово — байт — байт — байт, и очередь не используется. Когда используется 8-битовая шина для передачи команд процессору, читаются только байты, а очередь не используется и каждая выборка требует одного цикла шины.

Блок шинного интерфейса (ВШИ) осуществляет управление и определяет циклы шины, связанные с выборкой команд и передачей данных между СПВВ и памятью или УВВ. Каждое обращение к шине связано с битом регистра этикеток (регистр TAG находится в каждом канале), который указывает, к какому пространству адресов (системному или ввода — вывода) относится обращение. БШИ выставляет тип цикла шины (выборка команды из пространства адресов ввода — вывода, запись данных в память системного пространства и т.д.) в виде кода состояния на выходах S2 — S0 (табл. 2). Системный контроллер К1810ВГ88 декодирует этот код, выбирая нужную шину (СШ/ ШВВ) и формируя соответствующую команду (чтение, запись и т.д.). Затем БШИ определяет соотношение между логической и физической шириной СШ и LLIBB. Физическая ширина каждой шины фиксирована в системе и сообщается процессору или его инициализации.

| Код состояния S2SISO | Тип цикла шины |

| 000 001 010 011 100 101 110 111 | Выборка команды из пространства ввода - вывода Чтение данных из пространства ввода - вывода Запись данных в пространство ввода - вывода Не используется Выборка команды из системного пространства Чтение данных из системного пространства Запись данных в системное пространство Пассивное состояние |

Таблица 2.

В системной конфигурации обе шины (СШ и ШВВ) должны иметь одинаковую ширину: 8 или 16 бит, что определяется типом ЦП (ВМ86/ВМ88). В удаленной конфигурации СШ процессора ввода — вывода должна иметь ту же физическую ширину, что и СШ центрального процессора системы. Ширина ШВВ процессора ввода — вывода может быть выбрана независимо. Если в пространстве ввода — вывода используются какие-либо 16-битовые УВВ, должна использоваться 16- битовая ШВВ. Если в пространстве ввода — вывода все УВВ 8-битовые, то может быть выбрана 8- либо 16-битовая ШВВ. Преимущественно имеет 16- битовая ШВВ, поскольку она позволяет подключать к системе дополнительные 16-битовые УВВ, а также обеспечивает более эффективную выборку команд программы, размещенной в пространстве ввода — вывода.

Для ПДП-пересылки в программе канала задается логическая ширина СШ и ШВВ независимо для каждого канала. Логическая ширина 8-битовой физической шины может быть только 8- битовой, а для 16- битовой физической шины логическая ширина может быть задана 8- либо 16-битовой. Это позволяет обслуживать 8- и 16-битовые УВВ с помощью одной 16-битовой физической шины. В табл. 3 перечислены все возможные отношения между логической и физической шириной СШ и ШВВ в местной и удаленной конфигурации.

Таблица 3

| Конфигурация | Ширина СШ | Ширина | ШВВ |

| физическая логическая | физическая: | логическая | |

| Местная | 8:8 | 8: | |

| 16: (8/16) | 16: | (6/16) | |

| Удаленная | 8:8 | 8: | |

| 16: (8/16) | 16; | (8/16) | |

| 8:8 | 16: | (8/16) | |

| 16; (8/16) | 8: |

Логическая ширина шины учитывается только при ПДП - пересылках. Извлечение команд, а также запись и чтение операндов осуществляются словами или байтами только в зависимости от физической ширины шины.

Наряду с управлением пересылками команд и данных блок шинного интерфейса осуществляет арбитраж локальных шин. В местной конфигурации БШИ

Рекомендуем скачать другие рефераты по теме: реферат, баллов.

Предыдущая страница реферата | 1 2 3 4 5 6 7 8 9 10 11 | Следующая страница реферата