Разработка узла с функцией перевода чисел из формата в формат

Категория реферата: Рефераты по математике

Теги реферата: скачать доклад, семейные реферат

Добавил(а) на сайт: Меледин.

Предыдущая страница реферата | 1 2 3 4 5 | Следующая страница реферата

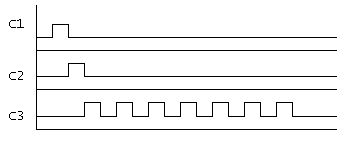

Входные данные подаются на регистр RG1 в параллельном виде. Для этого на входы D1-D8 подаем входные данные а на остальные: V1=V2=R=1, D(+)=D(-)=0. Тогда по приходу синхроимпульса C1 данные со входов D1-D8 будут занесены в регистр. Общая схема работы (с точки зрения синхроимпульсов) приведена ниже:

Затем, как видно из вышеприведенной схемы, данные с выходов 2-8 регистра RG1 поступают на входы D1-D7 регистра RG2, причем на вход D8 подается 0. Абсолютно аналогично, то есть подав V1=V2=R=1, D(+)=D(-)=0 мы заносим данные (это мантисса числа, которую нам надо нормализовать) по приходу синхроимпульса C2 в регистр RG2. По приходу этого же синхроимпульса в регистр RG4 заносится 7d=111b - это сразу смещенный порядок числа. Затем, начинается подача импульсов C3. Что же происходит при этом? Здесь начинает работать логика на элементах И-НЕ. То есть, проверяется содержится ли в старшем разряде мантиссы 0 (выход 1 регистра RG2). Если да, то сихнроимпульс приходит на регистры RG2 и RG4. Это приводит к тому, что мантисса, содержащаяся в регистре RG2 сдвигается на 1 разряд влево, а информация из регистра RG4 поступает на сумматор, где из порядка вычитается 1 и обратно заносится в регистр RG4. Таким образом мы разряд за разрядом нормализуем мантиссу. Когда в старшем разряде мантиссы окажется 1, то сработает логика на элементах И-НЕ и синхроимпульс C3 пойдет на регистр RG3, в который попадут выходные данные: старший разряд с регистра RG1 (знак), четыре разряда с регистра RG2 (мантисса) и три разряда с регистра RG4 (порядок). Для обеспечения работы регистра RG2 в параллельном и последовательном режиме на входе узла имеется управляющий вход V2. В начале работы, для обеспечения параллельного занесения из регистра RG1 в RG2 на вход V2 должна подаваться 1, а затем, для сдвига влево, должен подаваться 0. В регистре RG4, для обеспечения параллельного занесения на входы D0, V и C1 подается 1. Занесение 0111b (07d) в регистр RG4 происходит при появлении синхроимпульса C2, который не только обеспечивает занесение 7d в регистр порядка но и обеспечивает занесение в регистр RG2 мантиссы, а синхроимпульсы C3 отвечают за нормализацию мантиссы и за занесение выходных данных в регистр RG3 (это так сказать "выходной" регистр, с которого снимаются результаты преобразования).

Временная диаграмма для конкретного примера приводится в приложении, однако в несколько сокращенном виде поскольку полную временную диаграмму привести практически очень тяжело поскольку она будет занимать очень большой размер, да и это ненужно потому что некоторые внутренние входы/выходы практически никакой смысловой нагрузки не несут.

Более подробное описание логики (уже на основе конкретной схемы, приведенной в приложении и на основе позиционных обозначений микросхем) следует далее:

Как было описано выше, после появления синхроимпульса на входе XP6 (C1) входные данные с шины XP5 заносятся в регистр D1. После чего появляется сигнал XP8 (C2) который заносит значения 2-8 регистра D1 (мантисса) в регистр D2. Надо помнить, что при этом управляющий вход XP7 (управление регистром, V2) подана 1. Кроме того, сигнал XP8, проходит через логику на элементах D6.1-D6.3, D7.1-D7.3, которые появляются на входах d1-d3 регистра D4. После пропадания сигнала XP8 по заднему фронту в регистр D4 заносится значение 0111b (07d). Затем синхроимпульсы появляются на входе XP9 (C3). На логике D8.3 старший разряд регистра D2 инвертируется и поступает совместно с XP9 на элементы D6.4 и D7.4. Если в старшем разряде регистра D2 содержится 0, то данная логика сработает и на входах C1 регистра D4 и C регистра D2 возникнет синхроимпульс. На входе XP7 (управление регистром) у нас уже 0. Это приводит к тому, что значение в регистре D2 сдвинется влево на один разряд. Выходные данные с регистра D4 уже прошли через сумматор D5 и (всвязи с тем, что каждый четный выход у этого сумматора инверсный) логику на элементах D8.1, D8.2 поступили на вход регистра D4. В сумматоре данные складываются со значением 1111b (-1d), то есть фактически вычитается 1. Итак, эти данные уже поступили на вход регистра D4 и после прихода синхроимпульса на C2 эти данные в параллельном виде заносятся в регистр D4.

В эти же моменты времени у нас работает логика на элементах D8.4, D9.1, которая проверяет, а не появилась ли у нас в старшем разряде регистра D2 единица?

Пока в старшем разряде D2 будет появляться 0 - будет идти сдвиг мантиссы и вычитание из порядка 1. Но как только в старшем разряде регистра D2 появится 0, то сработает логика на элементах D6.4 и D7.4 которая прекратит подачу синхроимпульсов и преобразования над мантиссой и порядком. С другой стороны, сработает логика на регистрах D8.4 и D9.1 и синхроимпульс XP9 (C3) появится на входе регистра D3, что приведет к занесению результатов преобразования в регистр D3 (старший разряд из регистра D1 - знак, 4 разряда из регистра D2 - мантисса и 3 разряда из регистра D4 - порядок).

Все преобразования закончились и узел готов к следующему преобразованию.

Возможен также альтернативный вариант схемы: вместо связки регистр-сумматор можно использовать синхронный вычитающий счетчик с возможностью параллельного занесения информации. Тогда порядок подавался бы в на этот счетчик, а при преобразовании (сдвиге) мантиссы из порядка вычиталась бы 1. Данный, альтернативный вариант хотя и на порядок проще, однако и работает он медленнее, так как вычитающий счетчик работает медленнее чем пара регистр-сумматор.

АНАЛИЗ БЫСТРОДЕЙСТВИЯВременная диаграмма для конкретного числа (1 0010 101) приведена в приложении, а мы займемся быстродействием.

1. Занесение данных в регистр D1 - 30 нс.

2. Занесение данных в регистры D2, D4:

а. D2: 30 нс.

б. D4: логика И-НЕ - 15+22 нс=37 нс и занесение в регистр 35 нс.

3. Работа логики D8.3: 22 нс; D8.4+D9.1=37 нс (просиходит

параллельно с пунктом 4a).

4. Обработка порядка и мантиссы:

а. Сдвиг в регистре D2: 30 нс.

б. Порядок: сумматор, логика И-НЕ, параллельное занесение

в регистр: 55+22+35=112

5. Занесение информации в регистр D3: 30 нс.

То есть при худшем раскладе - 6 преобразований над мантиссой и порядком, суммарное быстродействие узла:

30+72+112*6+30=804 нс.

То есть максимальная частота преобразования=1,24 МГц.

ЗАКЛЮЧЕНИЕВ данном курсовом проекте был разработан узел, который выполняет функцию перевода чисел из формата с фиксированной точкой в формат с плавающей точкой.

Рекомендуем скачать другие рефераты по теме: конспект урока 7 класс, реферат религия.

Предыдущая страница реферата | 1 2 3 4 5 | Следующая страница реферата