Логическое проектирование и минимизация

Категория реферата: Рефераты по информатике, программированию

Теги реферата: стандарты реферата, реферат на тему право

Добавил(а) на сайт: Антиох.

Предыдущая страница реферата | 9 10 11 12 13 14 15 16 17 18 19 | Следующая страница реферата

Рис.4.5 Временные диаграммы дешифратора адреса

С полученных временных диаграмм легко сосчитать дешифрованный адрес. Кроме того на полученной диаграмме выхода схемы можно наблюдать паразитный выброс - результат гонок возникающих с приходом кода 0100 на первом элементе И см.рис.4.4(а). Это вполне объяснимо поскольку разряды дешифрируемого сигнала проходят разное количество цифровых элементов. Конечно у реальных дешифраторов обязательно используется строб-импульс или тактирование.

4.4 Схема контроля чётности

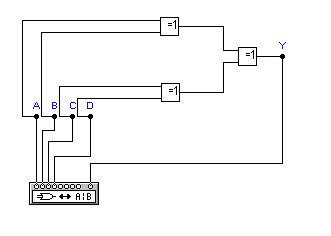

Рис.4.6 Схема для получения таблицы истинности бита чётности с помощью логического конвертора

Схема на рис.4.6 показывает способ подключения логического конвертора. При таком подключении и задании соответствующего режима работы цифровой конвертор составляет таблицу истинности для подключенной схемы. Происходит это следующим образом:

На своих выводах подключенных ко входам схемы конвертор перебирает все возможные сочетания 0 и 1. В данном случае подключено 4 входа следовательно это будет 24=16 комбинаций(4-х разрядных слов). С выхода схемы конвертор считывает реакцию схемы на каждое слово и записывает её в столбец Out отображённый на панели управления вместе с перебираемым входным кодом. Отклик схемы на каждое слово записывается в той же строке, где находится и само посланное слово.

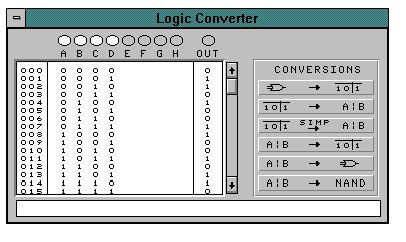

Таблица истинности для приведённой на рис.4.6 схемы контроля чётности будет иметь вид см.рис.4.7.

Рис.4.7 Таблица истинности схемы контроля чётности на панели логического конвертора.

Следующий этап - синтез схемы в базисе доступном на логическом конверторе.

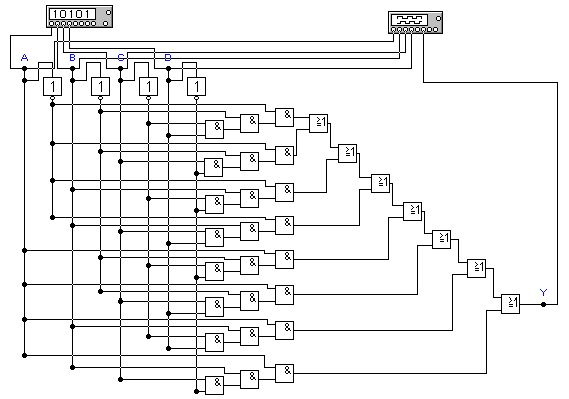

Рис.4.8 Схема контроля чётности синтезированная в базисе И, ИЛИ, НЕ

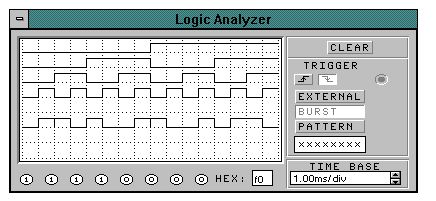

Представленная на рис.4.8 схема осуществляет контроль чётности поступающих на её входы 4-х разрядных слов. В случае если количество единиц чётное на выходе Y формируется 1 если нечётное 0. В этом можно убедится подключив генератор слов и логический анализатор как показано на схеме рис.4.8. Временные диаграммы полученные на логическом анализаторе имеют вид см.рис.4.9

Рис.4.9 Временные диаграммы схемы контроля чётности

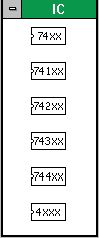

Все представленные здесь логические схемы реализованы на идеальных цифровых ключах из библиотеки Electronics Workbench. При желании их можно легко перевести в реальные серии микросхем. Библиотека Electronics Workbench предоставляет большие возможности для этого см.рис.4.10

Рис.4.10 Библиотека реальных компонентов электрических схем

Библиотека предоставляет широчайший набор цифровых компонентов ТТЛШ и КМОП технологий (ТТЛ логика морально устарела и поэтому не представлена).

5. Методические указания

к лабораторной работе.

“Логическое проектирование комбинационных схем.”

Цель работы: Изучить способы проектирования комбинационных схем с использованием с использованием логического конвертора моделирующего пакета программ Electronics Workbench.

Рекомендуем скачать другие рефераты по теме: бесплатные рефераты на тему, курсовик.

Предыдущая страница реферата | 9 10 11 12 13 14 15 16 17 18 19 | Следующая страница реферата